5.0 Virtual Memory

Definitions:

Ø

The main memory can act as a “chche” for the secondary storage,usually

implemented with magnetic disks.

Two

major motivations :

i.

Efficient and safe sharing

of main

memory among multiple programs.

ii.

Remove the programming burdens of a small, limited amount of main memory.

Ø Large

virtual address space

·

Mapping mechanism to

physical main memory.

ü E.g.

64 bit virtual address space.

ü Smaller

physical address – 36-40 bits common now.

Ø Multiple

process management

·

Each process has a “private” and “protected” virtual address space.

ü But

share physical memory (caches and main memory.

ü Trick

is how to manage this private/protected illusion so it’s true.

ü For

caches – virtual indexed and tagged via address spaces.

Ø Between

DRAM and disk

·

Miss becomes a page or

TLB fault.

ü TLB

is just a chche of recently used page table entries .

·

Block becomes a page or

segment.

Ø The

hardware ensures that one process cannot access the memory of a different

process.

Basic

Issues in Virtual Memory

v Size of data blocks that are transferred from disk to main

memory.

v Which region of memory to hold new

block.

=> placement policy

v When memory is full, then some region

of memory must be released to make room for the new block .

=> replacement

policy

v When to fetch missing items from

disk?

– Fetch only on a fault => demand load policy

Disk & Real

Memories

Ø Main

memory (physical memory) can act as a cache for the secondary storage (disk).

·

A virtual memory block

is called a page, and

·

A virtual memory miss

is called a page fault.

Ø This

process is called address mapping or address translation.

Ø Advantages:

·

Illusion of having more

and contiguous physical memory.

·

Program relocation by

“pages”.

·

Protection in

multiprogramming.

Address Translation

Ø Page table is lookup table for mapping virtual page # to physical

address.

Ø Located in memory.

Ø Each instruction execution refers to memory _ 1.35 times, so PT is

in cache, called translation lookaside buffer (TLB).

Ø The

address is broken into a virtual page number and a page

offset.

Ø The

translation of the virtual page number to a physical page number.

Ø The

physical page number constitutes the upper portion of the physical address.

§ While

the pages offset, which is not changed, constitutes the lower portion.

Ø Having

a larger number of virtual pages than physical pages

§ the

basis for the illusion of an essentially unbounded amount of virtual memory.

Address Translation

Cache: TLB

Ø Traditionally

referred to as a translation-lookaside buffer (TLB).

Ø Some typical valus for a TLB might be

§ TLB size: 16 – 512 entries

§ Block size: 1 – 2 page table entries (typically 4-8bytes each)

§ Hit time: 0.5 – 1 clock cycle

§ Miss penalty: 10 – 100 clock cycles

§ Miss rate: 0.01% - 1%

Ø The TLB has many fewer entries than the number of pages in main

memory, TLB misses will be much more frequent than true pages faults.

Ø TLB misses can be handled either in hardware or in software.

Implementing Protection

with Virtual Memory

Ø To

allow sharing of a single main memory by multiple processes.

·

While providing memory

protection among these processes and the operating system.

Ø The

hardware must provide at least the three basic capabilities summarized .

I.

Supervisor

process,kernel process, or an executive process.

·

Supervisor mode - called kernel mode. A mode indicating that a

running process is an operation system process.

II.

The includes the

user/supervisor mode bit, which dicates whether the processor is in

user/supervisor mode, the page table pointer, and the TLB.

III.

Typically accomplished

by a system call exception,implemented as a special instruction that transfers

control to a dedicated location in supervisor code space.

·

System call – a special

instruction that transfers control from user mode to a dedicated location in

supervisor code space, invoking the exception mechanism in the process.

Handling TLB Misses and

Page Faults

Ø The

translation of virtual to physical address with a TLB is straight forward when

we get a TLB hit, handling TLB misses and page faults is more complex.

Ø TLB

miss occurs when no entry in the TLB matches a virtual address.

Ø TLB

miss can indicate one of two possibilities:

a) The page is present in memory, and create the

missing TLB entry.

b) The

page is not present in memory,and need to transfer control to the operating

system to deal with a page fault.

Ø Prevent

the write into memory from actually completing when there is a page fault

·

Usually done by

deasserting the write control line to the memory.

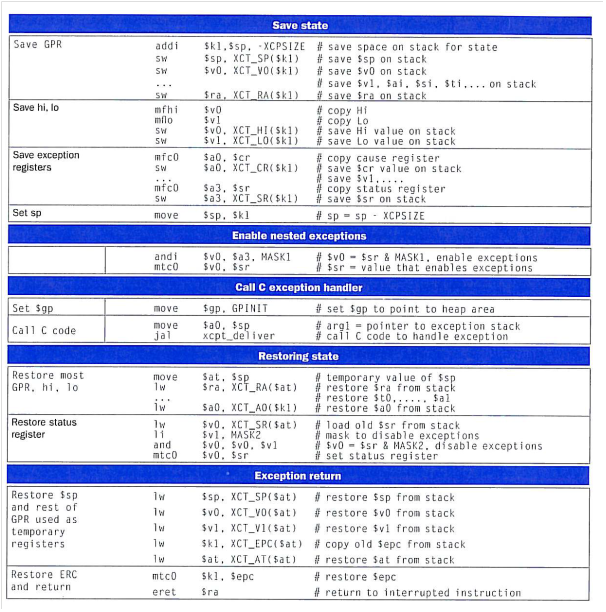

MIPS control registers

MIPS code to save and

restore on an exception

Ø The

simplified version assumes that the stack pointer (sp) is valid.

Ø To

avoid the problem of a page fault during this low-level exception code,MIPS

sets aside a portion of its address space that cannot have page faults,called unmapped.

§ Unmapped

– A portion of the address space that cannot have page faults.

Ø The

operating system places the exception entry point code and exception stack is

unmapped memory.

§ MIPS

hardware translates virtual address 8000 0000hex to BFFF FFFFhex

to physical addresses simply by ignoring the upper bits of the virtual

address,thereby placing these addresses in the low part of physical memory.

Ø The

operation system places exception entry points and exception stacks in unmapped

memory.

MIPS code to save and

restore on an exception

Paging

& Segmentation

Paging

§ Fixed

sized blocks. Address map contains base address.

§ Simple

replacement strategy (all blocks the same size)

§ Internal

fragmentation (not all addresses of a page are used)

§ One

(or very few) page tables per process – difficult to share segments of program.

Segmentation

·

Variable sized blocks. Address maps

contain base address and length.

·

Complex replacement (may be difficult to

find space of right size in memory)

·

External fragmentation (holes created in

main memory because of difficulties in allocation and replacement)

·

Many segments per process – easy to

share components of a program.

·

Segment table :

ü Segment

– offset in segment table

ü Pointer

to head of segment table required

·

Lots of segments – bigger segment table

required.

Summary

·

Virtual memory is used for relocatability & protection.

·

Virtual memory supports

sharing of the main memory among multiple, simulataneously active processes, in

a protected manner.

·

Page Tables are used for

virtual to real page address translation

·

Page tables map virtual address to

physical address.

·

TLBs are

caches for PT.

·

TLBs are important for fast translation.

·

TLB misses are

significant in processor performance.

·

The more complex

solution to reducing TLB misses is to re-examine the algorithm and data

structures to reduce the working set of pages.

§ Given

the importance of memory accesses to performance and the frequency of TLB

misses ,some programs with large working sets have been redesigned with that

goal.

·

Bottom level of memory hierarchy for programs.

·

Used in all general-purpose architectures.

Referenced by

3)

http://www.csie.nuk.edu.tw/~kcf/course/ComputerOrganization/ComputerOrganization_Chapter7_Memory.pdf

Written by,

YAU KAI SHI

B031210077

B031210077

No comments:

Post a Comment