Operations

of The Computer Hardware

- Every computer must be able to perform

arithmetic. Here, MIPS instruction set is used as example.

- MIPS assembly language notation:

add a, b, c # a = b + c (in c code) ** all arithmetic operations have this form.

- The words to the right of the # symbol

is meant for human reader(or known as comment), the computer will ignore them.

- This language(MIPS) can contain at most

one instruction, and must exactly three operand.

Example 1:

- In

C code, given, a= b + c + d + e.

- In

MIPS, is written as:

add

a, b, c # sum of b and c is placed

in a.

add

a, a, d #sum of b, c, and d is

placed in a

add

a, a, e #sum of b, c, d, and e is

placed in a

Example 2:

·

Given in C code, f = (g+h)-(i+j)

·

Then, in MIPS compiled code :

add

t0, g, h # temp t0 = g + h

add

t1, i, j # temp t1 = I + j

sub

f, t0, t1 # f = t0 – t1

- This shows that the MIPS language will

only do one process in a time.

·

This situation illustrates the first of

four underlying principles of hardware design:

-

Design principle 1: simplicity favors regularity.

Operands

of Computer hardware

Register

operand

·

Operand of arithmetic instruction of

MIPS must be from a limited number of special locations built directly in

hardware, called registers.

·

Registers are primitives used in hardware

design that are also visible to the programmer when the computer is completed.

·

The size of a register in MIPS

architecture is 32 bits, they are given name, word.

·

The difference between the variables of

a programming language and registers is limited number of registers, that is

32, as the second of four underlying design principle state that smaller

is faster.

-Large number of register may increase

the clock cycle time because it takes electronic signals longer when they must

travel farther.

·

Register is represented by two-character

names following a dollar sign, for example, $s0, $s1, $t0, $t1… etc.

·

The syntax is written as:

op

rd rs1 rs2

op = operation

rd = registered destination

rs 1 and rs 2 = register source 1 and 2

Example:

f = (g + h) – ( i + j)

add $t0, $s1, $s2 # this instruction means $t0 = x , $s1 = g , $s2 = h, x = g + h

add $t1, $s3, $s4 # this instruction means $t1 = y , $s3 = i , $s4 = j , y = i + j

sub $s0, $t0, $t1 # this instruction means $s0 = f , $t0 = x , $t1 = y , f = x + y

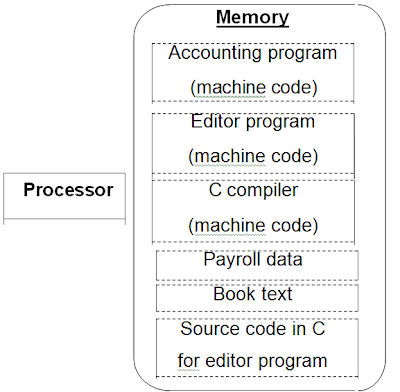

Memory

Operands

·

Programming languages also have more

complex data structures-arrays and structures which can contain many more data

elements than there are registers in computer.

·

These complex data structures are kept

in memory.

·

MIPS enable transfer data between memory

and register, this is called data transfer instructions.

·

To access words in memory, instruction

must supply the memory address.

·

Memory is just a large,

single-dimensional array, with address acting as index to the array, starting

at 0.

·

The instruction that copy data from

memory to a register is called load.

·

Format writing load instruction:

(actually MIPS name for it is lw, load word)

-operation

name(lw), then register to be loaded (eg: $s1), then constant and register used

to access memory.

·

Sum of constant portion of instruction

and contents of the second register forms memory address.

·

The compiler allocates data structures

to locations in memory, so that it can place proper starting address into the

data transfer instructions.

·

In MIPS, words must start at addresses

that are multiples of 4, this is called alignment

restriction.

·

This instruction complementary to load is call store, which copy data from a register to memory.

·

The actual name in MIPS is sw, store

word.

·

If a data is not exist in main memory,

it must be load to the register, after having the result from register, store

it in memory.

·

Example:

A[12] = h + A[8]

index

8 require 32 offset, multiply it by 4 as there are 4 bytes per word.

lw $t0, 32 ( $s3 ) #load word

add

$t0, $s2, $t0

sw $t0, 48 ( $s3) #store word

Constant/

immediate operands

·

The constant is added. For example,

1,2,3 etc.

·

The quick add instruction with one

constant operand is called add immediate

or addi.

·

There is no subi.

Example1

:

x

= y + 4

written

as, addi $s3, $s3, 4 # first $s3= x, second $s3 = y

Example2:

x = y – 1

since

there is no subi, so it is written as :

addi

$s3, $s3, -1

·

Immediate instructions illustrate the

third design principle, make the common fast.

-small

constants are common.

-immediate

operand avoid load instruction.

Signed

and unsigned numbers

·

Computer only read numbers of based two,

or, binary digits.

·

Example : 1011 based2 equal to 11

based10.

·

The number of bits are numbered from

right to left.

16 15

14 13

|

12 11

10 9

|

8 7

6 5

|

4 3

2 1

|

0 0

0 0

|

0 0

0 0

|

0 0

0 0

|

1 0

1 1

|

Unsigned

binary integers

x = xn-12n-1 + xn-22n-2 + … + x121 +

x020

·

Numbers have infinite number of digit,

with almost all 0, except for a few of the rightmost digits.

·

Hardware designed to add, subtract,

multiply and divide. If the number cannot be represented by these rightmost

hardware bits, overflow occur.

Signed

Binary Integers

·

Leading 0s means positive, whereas

leading 1s means negative. This convention is called two’s complement

representation.

·

x = - xn-12n-1 + xn-22n-2 + … + x12x + x020

·

After converting the 0 to 1, 1 to 0, add

the words by 1.

·

For example:

+1

= 0000 0000 0000 0000 0000 0000 0000 0001

In

order to get -1, convert it to 1111 1111 1111 1111 1111 1111 1111 1110, then

add 1.

So,

-1= 1111 1111 1111 1111 1111 1111 1111 1111

Reference:

Computer Organization

and Design, by David A. Patterson, John L. Hennessy

Written by,

Quek Xin Yi

B031210203